MIPI Screen

- Configure PAD to TTL mode

# vi infinity2m-ssc011a-s01a-padmux-display.dtsi

/*

* infinity2m-ssc011a-s01a-padmux-display.dtsi- Sigmastar

*

* Copyright (c) [2019~2020] SigmaStar Technology.

*

*

* This software is licensed under the terms of the GNU General Public

* License version 2, as published by the Free Software Foundation, and

* may be copied, distributed, and modified under those terms.

*

* This program is distributed in the hope that it will be useful,

* but WITHOUT ANY WARRANTY; without even the implied warranty of

* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

* GNU General Public License version 2 for more details.

*

*/

#include <../../../../drivers/sstar/include/infinity2m/padmux.h>

#include <../../../../drivers/sstar/include/mdrv_puse.h>

/ {

soc {

padmux {

compatible = "sstar-padmux";

schematic =

//<PAD_GPIO0 >,

<PAD_GPIO1 PINMUX_FOR_GPIO_MODE MDRV_PUSE_I2C1_DEV_RESET >,

<PAD_GPIO2 PINMUX_FOR_I2C1_MODE_1 MDRV_PUSE_I2C1_SCL >,

<PAD_GPIO3 PINMUX_FOR_I2C1_MODE_1 MDRV_PUSE_I2C1_SDA >,

//<PAD_GPIO4 PINMUX_FOR_PWM0_MODE_3 MDRV_PUSE_PWM0 >,

//<PAD_GPIO5 PINMUX_FOR_PWM1_MODE_4 MDRV_PUSE_PWM1 >,

//<PAD_GPIO6 PINMUX_FOR_EJ_MODE_3 MDRV_PUSE_EJ_TDO >,

//<PAD_GPIO7 PINMUX_FOR_EJ_MODE_3 MDRV_PUSE_EJ_TDI >,

//<PAD_GPIO6 PINMUX_FOR_I2C1_MODE_4 MDRV_PUSE_I2C1_SCL >,

//<PAD_GPIO7 PINMUX_FOR_I2C1_MODE_4 MDRV_PUSE_I2C1_SDA >,

//<PAD_GPIO10>,

<PAD_GPIO6 PINMUX_FOR_I2C0_MODE_4 MDRV_PUSE_I2C0_SCL >,

<PAD_GPIO7 PINMUX_FOR_I2C0_MODE_4 MDRV_PUSE_I2C0_SDA >,

<PAD_GPIO11 PINMUX_FOR_GPIO_MODE MDRV_PUSE_I2CSW_SCL>,

<PAD_GPIO12 PINMUX_FOR_GPIO_MODE MDRV_PUSE_AIO_AMP_PWR>,

<PAD_GPIO13 PINMUX_FOR_GPIO_MODE MDRV_PUSE_I2C1_DEV_IRQ >,

<PAD_FUART_RX PINMUX_FOR_FUART_MODE_2 MDRV_PUSE_FUART_RX>,

<PAD_FUART_TX PINMUX_FOR_FUART_MODE_2 MDRV_PUSE_FUART_TX>,

<PAD_FUART_CTS PINMUX_FOR_GPIO_MODE MDRV_PUSE_FUART_CTS>,

<PAD_FUART_RTS PINMUX_FOR_GPIO_MODE MDRV_PUSE_FUART_RTS>,

//RGB

#if 0

<PAD_TTL0 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT00 >,

<PAD_TTL1 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT01 >,

<PAD_TTL2 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT02 >,

<PAD_TTL3 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT03 >,

<PAD_TTL4 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT04 >,

<PAD_TTL5 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT05 >,

<PAD_TTL6 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT06 >,

<PAD_TTL7 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT07 >,

<PAD_TTL8 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT08 >,

<PAD_TTL9 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT09 >,

<PAD_TTL10 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT10 >,

<PAD_TTL11 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT11 >,

<PAD_TTL12 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT12 >,

<PAD_TTL13 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT13 >,

<PAD_TTL14 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT14 >,

<PAD_TTL15 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT15 >,

<PAD_TTL16 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT16 >,

<PAD_TTL17 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT17 >,

<PAD_TTL18 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT18 >,

<PAD_TTL19 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT19 >,

<PAD_TTL20 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT20 >,

<PAD_TTL21 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT21 >,

<PAD_TTL22 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT22 >,

<PAD_TTL23 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DOUT23 >,

<PAD_TTL24 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_CLK >,

<PAD_TTL25 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_HSYNC >,

<PAD_TTL26 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_VSYNC >,

<PAD_TTL27 PINMUX_FOR_TTL_MODE_1 MDRV_PUSE_TTL_DE >,

#endif

//MIPI 4lane

#if 1

<PAD_TTL6 PINMUX_FOR_TX_MIPI_MODE_1 MDRV_PUSE_TX_MIPI_P_CH0 >,

<PAD_TTL7 PINMUX_FOR_TX_MIPI_MODE_1 MDRV_PUSE_TX_MIPI_N_CH0 >,

<PAD_TTL8 PINMUX_FOR_TX_MIPI_MODE_1 MDRV_PUSE_TX_MIPI_P_CH1 >,

<PAD_TTL9 PINMUX_FOR_TX_MIPI_MODE_1 MDRV_PUSE_TX_MIPI_N_CH1 >,

<PAD_TTL10 PINMUX_FOR_TX_MIPI_MODE_1 MDRV_PUSE_TX_MIPI_P_CH2 >,

<PAD_TTL11 PINMUX_FOR_TX_MIPI_MODE_1 MDRV_PUSE_TX_MIPI_N_CH2 >,

<PAD_TTL12 PINMUX_FOR_TX_MIPI_MODE_1 MDRV_PUSE_TX_MIPI_P_CH3 >,

<PAD_TTL13 PINMUX_FOR_TX_MIPI_MODE_1 MDRV_PUSE_TX_MIPI_N_CH3 >,

<PAD_TTL14 PINMUX_FOR_TX_MIPI_MODE_1 MDRV_PUSE_TX_MIPI_P_CH4 >,

<PAD_TTL15 PINMUX_FOR_TX_MIPI_MODE_1 MDRV_PUSE_TX_MIPI_N_CH4 >,

#endif

//<PAD_UART0_RX PINMUX_FOR_UART0_MODE_1 MDRV_PUSE_UART0_RX >,

<PAD_UART0_TX PINMUX_FOR_UART0_MODE_1 MDRV_PUSE_UART0_TX >,

<PAD_UART1_RX PINMUX_FOR_UART1_MODE_1 MDRV_PUSE_UART1_RX >,

<PAD_UART1_TX PINMUX_FOR_UART1_MODE_1 MDRV_PUSE_UART1_TX >,

<PAD_GPIO8 PINMUX_FOR_UART2_MODE_2 MDRV_PUSE_UART2_RX >,

<PAD_GPIO9 PINMUX_FOR_UART2_MODE_2 MDRV_PUSE_UART2_TX >,

//<PAD_SD_CLK PINMUX_FOR_I2S_MODE_3 MDRV_PUSE_I2S_BCK >,

<PAD_GPIO0 PINMUX_FOR_GPIO_MODE MDRV_PUSE_SDIO0_PWR >,

<PAD_SD_CLK PINMUX_FOR_SDIO_MODE_1 MDRV_PUSE_SDIO0_CLK >,

<PAD_SD_CMD PINMUX_FOR_SDIO_MODE_1 MDRV_PUSE_SDIO0_CMD >,

<PAD_SD_D0 PINMUX_FOR_SDIO_MODE_1 MDRV_PUSE_SDIO0_D0 >,

<PAD_SD_D1 PINMUX_FOR_SDIO_MODE_1 MDRV_PUSE_SDIO0_D1>,

<PAD_SD_D2 PINMUX_FOR_SDIO_MODE_1 MDRV_PUSE_SDIO0_D2>,

<PAD_SD_D3 PINMUX_FOR_SDIO_MODE_1 MDRV_PUSE_SDIO0_D3>,

<PAD_PM_SD_CDZ PINMUX_FOR_GPIO_MODE MDRV_PUSE_SDIO0_CDZ>,

<PAD_PM_IRIN PINMUX_FOR_PM_IRIN_MODE MDRV_PUSE_IR>, // IR: default non-GPIO

//<PAD_PM_SPI_CZ >, // default not-GPIO

//<PAD_PM_SPI_CK >, // default not-GPIO

//<PAD_PM_SPI_DI >, // default not-GPIO

//<PAD_PM_SPI_DO >, // default not-GPIO

//<PAD_PM_SPI_WPZ >, // default not-GPIO

//<PAD_PM_SPI_HLD >, // default not-GPIO

<PAD_PM_LED0 PINMUX_FOR_PM_LED_MODE_1 MDRV_PUSE_EMAC0_LED>,

<PAD_PM_LED1 PINMUX_FOR_PM_LED_MODE_1 MDRV_PUSE_EMAC0_LED>,

<PAD_SAR_GPIO0 PINMUX_FOR_SAR_MODE MDRV_PUSE_SAR_GPIO0 >, // sar: default not-GPIO,

//<PAD_SAR_GPIO1 >, // sar: default not-GPIO

//<PAD_ETH_RN >, // ETH: default not-GPIO

//<PAD_ETH_RP >, // ETH: default not-GPIO

//<PAD_ETH_TN >, // ETH: default not-GPIO

//<PAD_ETH_TP >, // ETH: default not-GPIO

<PAD_DM_P1 PINMUX_FOR_USB_MODE MDRV_PUSE_UTMI1_DM >, // utmi: default not-GPIO

<PAD_DP_P1 PINMUX_FOR_USB_MODE MDRV_PUSE_UTMI1_DP >, // utmi: default not-GPIO

<PAD_DM_P2 PINMUX_FOR_USB_MODE MDRV_PUSE_UTMI2_DM >, // utmi: default not-GPIO

<PAD_DP_P2 PINMUX_FOR_USB_MODE MDRV_PUSE_UTMI2_DP >, // utmi: default not-GPIO

//<PAD_HSYNC_OUT >,

//<PAD_VSYNC_OUT >,

<PAD_HDMITX_SCL PINMUX_FOR_DMIC_MODE_2 MDRV_PUSE_DMIC_D1 >,

<PAD_HDMITX_SDA PINMUX_FOR_DMIC_MODE_2 MDRV_PUSE_DMIC_D0 >,

<PAD_HDMITX_HPD PINMUX_FOR_DMIC_MODE_2 MDRV_PUSE_DMIC_CLK >,

<PAD_UART0_RX PINMUX_FOR_GPIO_MODE MDRV_PUSE_UART0_RX >;

//<PAD_HSYNC_OUT PINMUX_FOR_IDAC_MODE MDRV_PUSE_IDAC_HSYNC>,

//<PAD_VSYNC_OUT PINMUX_FOR_IDAC_MODE MDRV_PUSE_IDAC_VSYNC>;

//<PAD_SATA_GPIO >;

status = "ok"; // ok or disable

//status = "disable";

};

};

};

- Obtain the schedule from the data book on the screen

- Modify screen parameters

You can capy WT070BM24_800x1280_MIPI.h, Based on it, the modification method is the same as TTL screen.

#include "mi_panel_datatype.h"

#define FLAG_DELAY 0xFE

#define FLAG_END_OF_TABLE 0xFF // END OF REGISTERS MARKER

#define HPW (4)

#define HBP (54)

#define HFP (52)

#define VPW (18)

#define VBP (55)

#define VFP (60)

#define FPS (60)

#define HDA (800)

#define VDA (1280)

MI_PANEL_ParamConfig_t stPanelParam =

{

"WT070BM24_800x1280_60", // const char *m_pPanelName; ///< PanelName

0, //MS_U8 m_bPanelDither :1; ///< PANEL_DITHER, keep the setting

E_MI_PNL_LINK_MIPI_DSI, //MHAL_DISP_ApiPnlLinkType_e m_ePanelLinkType :4; ///< PANEL_LINK

///////////////////////////////////////////////

// Board related setting

///////////////////////////////////////////////

1, //MS_U8 m_bPanelDualPort :1; ///< VOP_21[8], MOD_4A[1], PANEL_DUAL_PORT, refer to m_bPanelDoubleClk

0, //MS_U8 m_bPanelSwapPort :1; ///< MOD_4A[0], PANEL_SWAP_PORT, refer to "LVDS output app note" A/B channel swap

0, //MS_U8 m_bPanelSwapOdd_ML :1; ///< PANEL_SWAP_ODD_ML

0, //MS_U8 m_bPanelSwapEven_ML :1; ///< PANEL_SWAP_EVEN_ML

0, //MS_U8 m_bPanelSwapOdd_RB :1; ///< PANEL_SWAP_ODD_RB

0, //MS_U8 m_bPanelSwapEven_RB :1; ///< PANEL_SWAP_EVEN_RB

0, //MS_U8 m_bPanelSwapLVDS_POL :1; ///< MOD_40[5], PANEL_SWAP_LVDS_POL, for differential P/N swap

0, //MS_U8 m_bPanelSwapLVDS_CH :1; ///< MOD_40[6], PANEL_SWAP_LVDS_CH, for pair swap

0, //MS_U8 m_bPanelPDP10BIT :1; ///< MOD_40[3], PANEL_PDP_10BIT ,for pair swap

1, //MS_U8 m_bPanelLVDS_TI_MODE :1; ///< MOD_40[2], PANEL_LVDS_TI_MODE, refer to "LVDS output app note"

///////////////////////////////////////////////

// For TTL Only

///////////////////////////////////////////////

0, //MS_U8 m_ucPanelDCLKDelay; ///< PANEL_DCLK_DELAY

0, //MS_U8 m_bPanelInvDCLK :1; ///< MOD_4A[4], PANEL_INV_DCLK

0, //MS_U8 m_bPanelInvDE :1; ///< MOD_4A[2], PANEL_INV_DE

0, //MS_U8 m_bPanelInvHSync :1; ///< MOD_4A[12], PANEL_INV_HSYNC

0, //MS_U8 m_bPanelInvVSync :1; ///< MOD_4A[3], PANEL_INV_VSYNC

///////////////////////////////////////////////

// Output driving current setting

///////////////////////////////////////////////

// driving current setting (0x00=4mA, 0x01=6mA, 0x02=8mA, 0x03=12mA)

1, //MS_U8 m_ucPanelDCKLCurrent; ///< define PANEL_DCLK_CURRENT

1, //MS_U8 m_ucPanelDECurrent; ///< define PANEL_DE_CURRENT

1, //MS_U8 m_ucPanelODDDataCurrent; ///< define PANEL_ODD_DATA_CURRENT

1, //MS_U8 m_ucPanelEvenDataCurrent; ///< define PANEL_EVEN_DATA_CURRENT

///////////////////////////////////////////////

// panel on/off timing

///////////////////////////////////////////////

30, //MS_U16 m_wPanelOnTiming1; ///< time between panel & data while turn on power

400, //MS_U16 m_wPanelOnTiming2; ///< time between data & back light while turn on power

80, //MS_U16 m_wPanelOffTiming1; ///< time between back light & data while turn off power

30, //MS_U16 m_wPanelOffTiming2; ///< time between data & panel while turn off power

///////////////////////////////////////////////

// panel timing spec.

///////////////////////////////////////////////

// sync related

HPW, //MS_U8 m_ucPanelHSyncWidth; ///< VOP_01[7:0], PANEL_HSYNC_WIDTH

HBP, //MS_U8 m_ucPanelHSyncBackPorch; ///< PANEL_HSYNC_BACK_PORCH, no register setting, provide value for query only

///< not support Manuel VSync Start/End now

///< VOP_02[10:0] VSync start = Vtt - VBackPorch - VSyncWidth

///< VOP_03[10:0] VSync end = Vtt - VBackPorch

VPW, //MS_U8 m_ucPanelVSyncWidth; ///< define PANEL_VSYNC_WIDTH

VBP, //MS_U8 m_ucPanelVBackPorch; ///< define PANEL_VSYNC_BACK_PORCH

// DE related

(HPW+HBP), //MS_U16 m_wPanelHStart; ///< VOP_04[11:0], PANEL_HSTART, DE H Start (PANEL_HSYNC_WIDTH + PANEL_HSYNC_BACK_PORCH)

(VPW+VBP), //MS_U16 m_wPanelVStart; ///< VOP_06[11:0], PANEL_VSTART, DE V Start

HDA, //MS_U16 m_wPanelWidth; ///< PANEL_WIDTH, DE width (VOP_05[11:0] = HEnd = HStart + Width - 1)

VDA, //MS_U16 m_wPanelHeight; ///< PANEL_HEIGHT, DE height (VOP_07[11:0], = Vend = VStart + Height - 1)

// DClk related

0, //MS_U16 m_wPanelMaxHTotal; ///< PANEL_MAX_HTOTAL. Reserved for future using.

(HDA+HPW+HBP+HFP), //MS_U16 m_wPanelHTotal; ///< VOP_0C[11:0], PANEL_HTOTAL

0, //MS_U16 m_wPanelMinHTotal; ///< PANEL_MIN_HTOTAL. Reserved for future using.

0, //MS_U16 m_wPanelMaxVTotal; ///< PANEL_MAX_VTOTAL. Reserved for future using.

(VDA+VPW+VBP+VFP), //MS_U16 m_wPanelVTotal; ///< VOP_0D[11:0], PANEL_VTOTAL

0, //MS_U16 m_wPanelMinVTotal; ///< PANEL_MIN_VTOTAL. Reserved for future using.

0, //MS_U8 m_dwPanelMaxDCLK; ///< PANEL_MAX_DCLK. Reserved for future using.

((unsigned long)(VDA+VPW+VBP+VFP)*(HDA+HPW+HBP+HFP)*FPS/1048576), //MS_U8 m_dwPanelDCLK; ///< LPLL_0F[23:0], PANEL_DCLK ,{0x3100_10[7:0], 0x3100_0F[15:0]}

0, //MS_U8 m_dwPanelMinDCLK; ///< PANEL_MIN_DCLK. Reserved for future using.

///< spread spectrum

0, //MS_U16 m_wSpreadSpectrumStep; ///< move to board define, no use now.

0, //MS_U16 m_wSpreadSpectrumSpan; ///< move to board define, no use now.

160, //MS_U8 m_ucDimmingCtl; ///< Initial Dimming Value

255, //MS_U8 m_ucMaxPWMVal; ///< Max Dimming Value

80, //MS_U8 m_ucMinPWMVal; ///< Min Dimming Value

0, //MS_U8 m_bPanelDeinterMode :1; ///< define PANEL_DEINTER_MODE, no use now

E_MI_PNL_ASPECT_RATIO_WIDE, //MHAL_DISP_PnlAspectRatio_e m_ucPanelAspectRatio; ///< Panel Aspect Ratio, provide information to upper layer application for aspect ratio setting.

/*

*

* Board related params

*

* If a board ( like BD_MST064C_D01A_S ) swap LVDS TX polarity

* : This polarity swap value =

* (LVDS_PN_SWAP_H<<8) | LVDS_PN_SWAP_L from board define,

* Otherwise

* : The value shall set to 0.

*/

0, //MS_U16 m_u16LVDSTxSwapValue;

E_MI_PNL_TI_8BIT_MODE, //MHAL_DISP_ApiPnlTiBitMode_e m_ucTiBitMode; ///< MOD_4B[1:0], refer to "LVDS output app note"

E_MI_PNL_OUTPUT_8BIT_MODE, //MHAL_DISP_ApiPnlOutPutFormatBitMode_e m_ucOutputFormatBitMode;

0, //MS_U8 m_bPanelSwapOdd_RG :1; ///< define PANEL_SWAP_ODD_RG

0, //MS_U8 m_bPanelSwapEven_RG :1; ///< define PANEL_SWAP_EVEN_RG

0, //MS_U8 m_bPanelSwapOdd_GB :1; ///< define PANEL_SWAP_ODD_GB

0, //MS_U8 m_bPanelSwapEven_GB :1; ///< define PANEL_SWAP_EVEN_GB

/**

* Others

*/

1, //MS_U8 m_bPanelDoubleClk :1; ///< LPLL_03[7], define Double Clock ,LVDS dual mode

0x001c848e, //MS_U32 m_dwPanelMaxSET; ///< define PANEL_MAX_SET

0x0018eb59, //MS_U32 m_dwPanelMinSET; ///< define PANEL_MIN_SET

E_MI_PNL_CHG_VTOTAL, //MHAL_DISP_ApiPnlOutTimingMode_e m_ucOutTimingMode; ///<Define which panel output timing change mode is used to change VFreq for same panel

0, //MS_U8 m_bPanelNoiseDith :1; ///< PAFRC mixed with noise dither disable

(MI_PANEL_ChannelSwapType_e)2,

(MI_PANEL_ChannelSwapType_e)4,

(MI_PANEL_ChannelSwapType_e)3,

(MI_PANEL_ChannelSwapType_e)1,

(MI_PANEL_ChannelSwapType_e)0,

/*

(MI_PANEL_ChannelSwapType_e)2,

(MI_PANEL_ChannelSwapType_e)4,

(MI_PANEL_ChannelSwapType_e)3,

(MI_PANEL_ChannelSwapType_e)1,

(MI_PANEL_ChannelSwapType_e)0,

*/

};

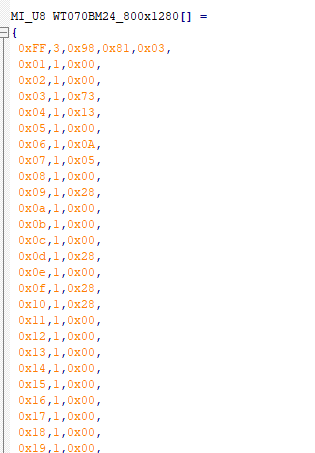

MI_U8 WT070BM24_800x1280[] =

{

0xFF,3,0x98,0x81,0x03,

0x01,1,0x00,

0x02,1,0x00,

0x03,1,0x73,

0x04,1,0x13,

0x05,1,0x00,

0x06,1,0x0A,

0x07,1,0x05,

0x08,1,0x00,

0x09,1,0x28,

0x0a,1,0x00,

0x0b,1,0x00,

0x0c,1,0x00,

0x0d,1,0x28,

0x0e,1,0x00,

0x0f,1,0x28,

0x10,1,0x28,

0x11,1,0x00,

0x12,1,0x00,

0x13,1,0x00,

0x14,1,0x00,

0x15,1,0x00,

0x16,1,0x00,

0x17,1,0x00,

0x18,1,0x00,

0x19,1,0x00,

0x1a,1,0x00,

0x1b,1,0x00,

0x1c,1,0x00,

0x1d,1,0x00,

0x1e,1,0x40,

0x1f,1,0x80,

0x20,1,0x06,

0x21,1,0x01,

0x22,1,0x00,

0x23,1,0x00,

0x24,1,0x00,

0x25,1,0x00,

0x26,1,0x00,

0x27,1,0x00,

0x28,1,0x33,

0x29,1,0x33,

0x2a,1,0x00,

0x2b,1,0x00,

0x2c,1,0x04,

0x2d,1,0x04,

0x2e,1,0x05,

0x2f,1,0x05,

0x30,1,0x00,

0x31,1,0x00,

0x32,1,0x31,

0x33,1,0x00,

0x34,1,0x00,

0x35,1,0x0A,

0x36,1,0x00,

0x37,1,0x08,

0x38,1,0x00,

0x39,1,0x00,

0x3a,1,0x00,

0x3b,1,0x00,

0x3c,1,0x00,

0x3d,1,0x00,

0x3e,1,0x00,

0x3f,1,0x00,

0x40,1,0x00,

0x41,1,0x00,

0x42,1,0x00,

0x43,1,0x08,

0x44,1,0x00,

0x50,1,0x01,

0x51,1,0x23,

0x52,1,0x44,

0x53,1,0x67,

0x54,1,0x89,

0x55,1,0xab,

0x56,1,0x01,

0x57,1,0x23,

0x58,1,0x45,

0x59,1,0x67,

0x5a,1,0x89,

0x5b,1,0xab,

0x5c,1,0xcd,

0x5d,1,0xef,

0x5e,1,0x11,

0x5f,1,0x02,

0x60,1,0x08,

0x61,1,0x0E,

0x62,1,0x0F,

0x63,1,0x0C,

0x64,1,0x0D,

0x65,1,0x17,

0x66,1,0x01,

0x67,1,0x01,

0x68,1,0x02,

0x69,1,0x02,

0x6a,1,0x00,

0x6b,1,0x00,

0x6c,1,0x02,

0x6d,1,0x02,

0x6e,1,0x16,

0x6f,1,0x16,

0x70,1,0x06,

0x71,1,0x06,

0x72,1,0x07,

0x73,1,0x07,

0x74,1,0x02,

0x75,1,0x02,

0x76,1,0x08,

0x77,1,0x0E,

0x78,1,0x0F,

0x79,1,0x0C,

0x7a,1,0x0D,

0x7b,1,0x17,

0x7c,1,0x01,

0x7d,1,0x01,

0x7e,1,0x02,

0x7f,1,0x02,

0x80,1,0x00,

0x81,1,0x00,

0x82,1,0x02,

0x83,1,0x02,

0x84,1,0x16,

0x85,1,0x16,

0x86,1,0x06,

0x87,1,0x06,

0x88,1,0x07,

0x89,1,0x07,

0x8A,1,0x02,

0xFF,3,0x98,0x81,0x04,

0x6E,1,0x1A,

0x6F,1,0x37,

0x3A,1,0xA4,

0x8D,1,0x1F,

0x87,1,0xBA,

0xB2,1,0xD1,

0x88,1,0x0B,

0x38,1,0x01,

0x39,1,0x00,

0xB5,1,0x02,

0x31,1,0x25,

0x3B,1,0x98,

0xFF,3,0x98,0x81,0x01,

0x22,1,0x0A,

0x31,1,0x00,

0x53,1,0x5A, //53

0x55,1,0x3D, //3D

0x50,1,0x9E,

0x51,1,0x99,

0x60,1,0x06,

0x62,1,0x20,

/*===========Gamma START=============*/

0xA0,1,0x00,

0xA1,1,0x17,

0xA2,1,0x26,

0xA3,1,0x13,

0xA4,1,0x16,

0xA5,1,0x29,

0xA6,1,0x1E,

0xA7,1,0x1F,

0xA8,1,0x8B,

0xA9,1,0x1D,

0xAA,1,0x2A,

0xAB,1,0x7B,

0xAC,1,0x1A,

0xAD,1,0x19,

0xAE,1,0x4E,

0xAF,1,0x24,

0xB0,1,0x29,

0xB1,1,0x4F,

0xB2,1,0x5C,

0xB3,1,0x23,

0xC0,1,0x00,

0xC1,1,0x17,

0xC2,1,0x26,

0xC3,1,0x13,

0xC4,1,0x16,

0xC5,1,0x29,

0xC6,1,0x1E,

0xC7,1,0x1F,

0xC8,1,0x8B,

0xC9,1,0x1D,

0xCA,1,0x2A,

0xCB,1,0x7B,

0xCC,1,0x1A,

0xCD,1,0x19,

0xCE,1,0x4E,

0xCF,1,0x24,

0xD0,1,0x29,

0xD1,1,0x4F,

0xD2,1,0x5C,

0xD3,1,0x23,

0xFF,3,0x98,0x81,0x00,

0x11,1,0x00,

FLAG_DELAY,FLAG_DELAY,250,

0x29,1,0x00,

FLAG_DELAY,FLAG_DELAY,200,

FLAG_END_OF_TABLE, FLAG_END_OF_TABLE,

};

MI_PANEL_MipiDsiConfig_t stMipiDsiConfig =

{

//HsTrail HsPrpr HsZero ClkHsPrpr ClkHsExit ClkTrail ClkZero ClkHsPost DaHsExit ContDet

5, 3, 5, 10, 14, 3, 12, 10, 5, 0,

//Lpx TaGet TaSure TaGo

16, 26, 24, 50,

//Hac, Hpw, Hbp, Hfp, Vac, Vpw, Vbp, Vfp, Bllp, Fps

HDA, HPW, HBP, HFP, VDA, VPW, VBP, VFP, 0, FPS,

E_MI_PNL_MIPI_DSI_LANE_4, // MIPnlMipiDsiLaneMode_e enLaneNum;

E_MI_PNL_MIPI_DSI_RGB888, // MIPnlMipiDsiFormat_e enFormat;

E_MI_PNL_MIPI_DSI_SYNC_PULSE, // MIPnlMipiDsiCtrlMode_e enCtrl;

WT070BM24_800x1280,

sizeof(WT070BM24_800x1280),

1, 0x01AF, 0x01B9, 0x80D2, 7,

};

- Modify the value of swap

(MI_PANEL_ChannelSwapType_e)2,

(MI_PANEL_ChannelSwapType_e)4,

(MI_PANEL_ChannelSwapType_e)3,

(MI_PANEL_ChannelSwapType_e)1,

(MI_PANEL_ChannelSwapType_e)0,

The default PAD pin and Mipi correspond to the following functions:

If the actual circuit connection is inconsistent, you need to modify the value of channelswap:

The revised rules are as follows:

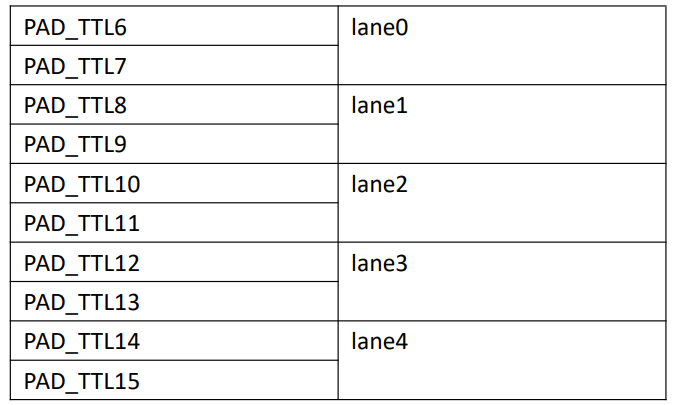

Firstly, pad and lane were grouped:

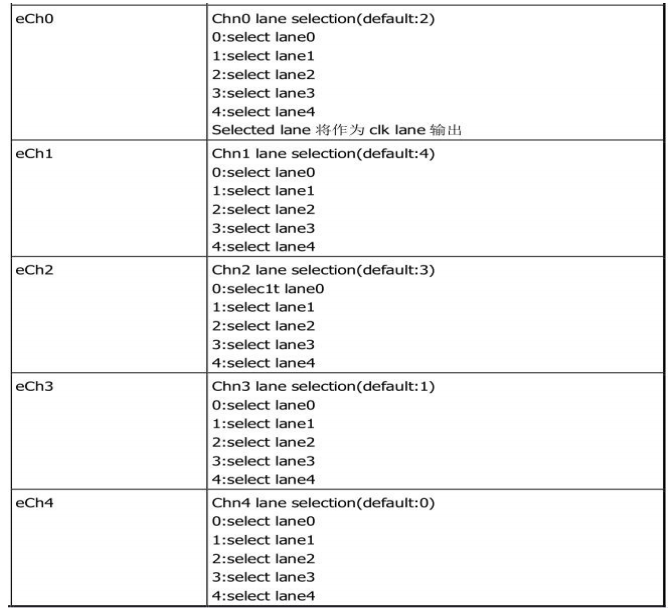

And understand the meaning of ech0-4

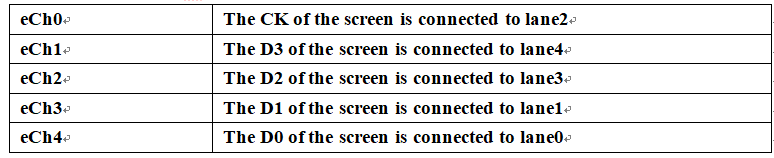

Here is an example. D0-d3 is respectively connected to the d0-d3 of the screen, and CK is connected to the ck of the screen. Therefore, the following table is obtained:

Modify the initialization array according to the initialization code provided by the screen manufacturer

Modify the value of stmipidsiconfig

MI_PANEL_MipiDsiConfig_t stMipiDsiConfig =

{

//HsTrail HsPrpr HsZero ClkHsPrpr ClkHsExit ClkTrail ClkZero ClkHsPost DaHsExit ContDet

5, 3, 5, 10, 14, 3, 12, 10, 5, 0,

//Lpx TaGet TaSure TaGo

16, 26, 24, 50,

//Hac, Hpw, Hbp, Hfp, Vac, Vpw, Vbp, Vfp, Bllp, Fps

HDA, HPW, HBP, HFP, VDA, VPW, VBP, VFP, 0, FPS,

E_MI_PNL_MIPI_DSI_LANE_4, // MIPnlMipiDsiLaneMode_e enLaneNum;

E_MI_PNL_MIPI_DSI_RGB888, // MIPnlMipiDsiFormat_e enFormat;

E_MI_PNL_MIPI_DSI_SYNC_PULSE, // MIPnlMipiDsiCtrlMode_e enCtrl;

WT070BM24_800x1280,

sizeof(WT070BM24_800x1280),

1, 0x01AF, 0x01B9, 0x80D2, 7,

文档更新时间: 2022-06-20 17:00 作者:Aeeditor