Chapter 15 I2C configuration

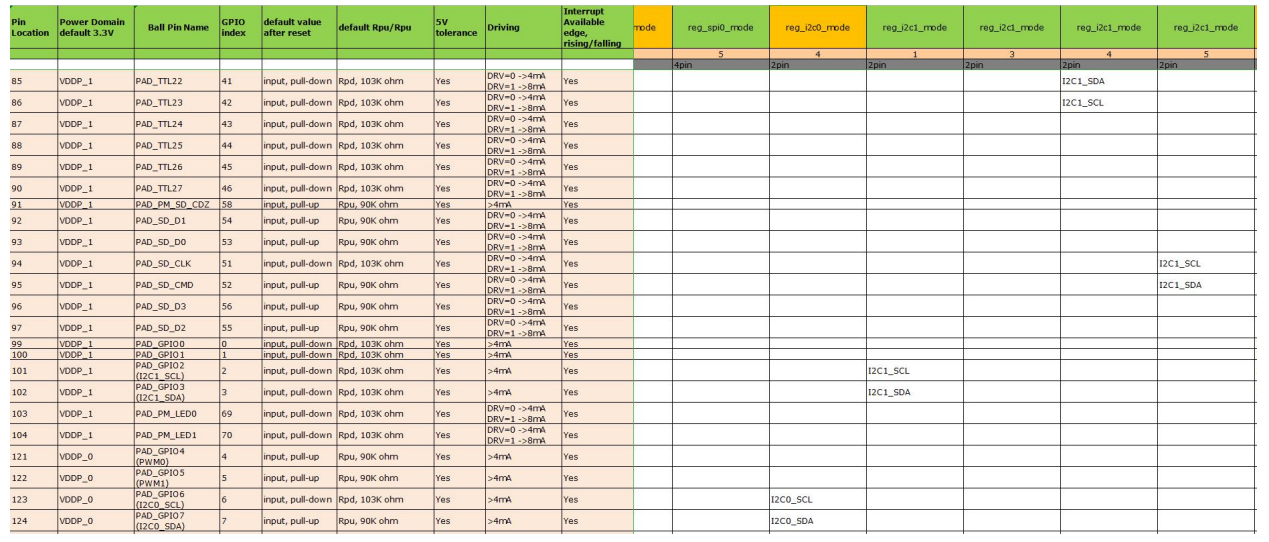

The SSD20X provides two sets of hardware I2C. According to the SSD201 HW Checklist V6.xlsx[GPIOList] table, we can see which pins I2C0 and I2C1 can reuse:

The data in the following table are summarized:

First configure the DTS I2C node:

vi arch/arm/boot/dts/infinity2m-ssc011a-s01a-display.dtsi i2c0@0{

compatible = "sstar,i2c";

reg = <0x1F223000 0x200>,<0x1F203c00 0x200>,<0x1F207000 0x200>;

#address-cells = <1>;

#size-cells = <0>;

clocks = <&CLK_miic0>;

i2c-group = <0>;

/*

* padmux: 1 -> PAD_HDMITX_SCL, PAD_HDMITX_SDA

* 2 -> PAD_TTL1, PAD_TTL2

* 3 -> PAD_TTL14, PAD_TTL15

* 4 -> PAD_GPIO6, PAD_GPIO7

*/

i2c-padmux = <4>;

/*

* speed: 0 -> HWI2C_HIGH(high speed: 400 KHz)

* 1 -> HWI2C_NORMAL(normal speed: 300 KHz)

* 2 -> HWI2C_SLOW(slow speed: 200 KHz)

* 3 -> HWI2C_VSLOW(very slow: 100 KHz)

* 4 -> HWI2C_USLOW(ultra slow: 50 KHz)

* 5 -> HWI2C_UVSLOW(ultra-very slow: 25 KHz)

*/

i2c-speed = <3>;

i2c-en-dma = <0>; // 0: disable; 1: enable;

status = "ok";

};Pay attention to which set of GPIOs is used and assign the value I2C -padmux.Then set the multiplexing mode of this group of GPIO:

vi infinity2m-ssc011a-s01a-padmux-display.dtsi

<PAD_GPIO6 PINMUX_FOR_I2C0_MODE_4 MDRV_PUSE_I2C0_SCL >,

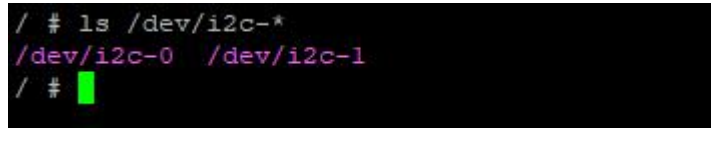

<PAD_GPIO7 PINMUX_FOR_I2C0_MODE_4 MDRV_PUSE_I2C0_SDA >,Once the system is up,You can see /dev/i2C-0,The driver was loaded successfully.

文档更新时间: 2021-10-08 10:46 作者:Aeeditor